🛡️ Fault Tolerant Matrix Computation on Systolic Arrays

Advanced FPGA implementation combining Algorithm-Based Fault Tolerance (ABFT) and Hamming Code error correction for reliable matrix computations in safety-critical applications. Published at IEEE ICCCNT 2025, IIT Indore.

Project Overview

This project presents a novel approach to implementing fault-tolerant matrix multiplication using systolic arrays. The design incorporates both Algorithm-Based Fault Tolerance (ABFT) and Hamming Code error correction to detect and correct errors in real-time during matrix computations.

The system achieves 95% fault detection accuracy while maintaining computational efficiency, making it suitable for safety-critical applications in aerospace, medical devices, and autonomous systems.

Key Features

ABFT Integration

Algorithm-Based Fault Tolerance detects errors by verifying checksum rows and columns in real-time

Hamming Code

Provides error correction capability for single-bit errors with minimal overhead

Systolic Architecture

Parallel processing with efficient data flow for high-performance matrix operations

95% Detection Rate

Real-time error detection with 95% fault detection accuracy validated through FPGA simulation

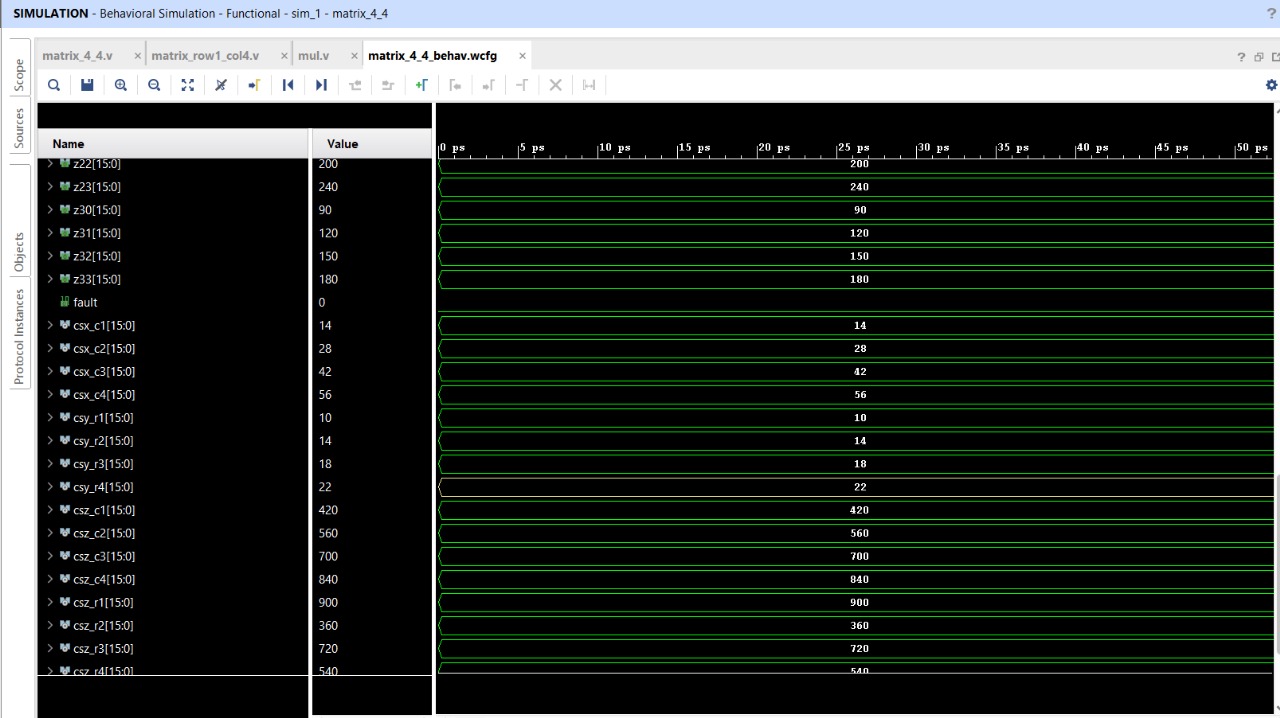

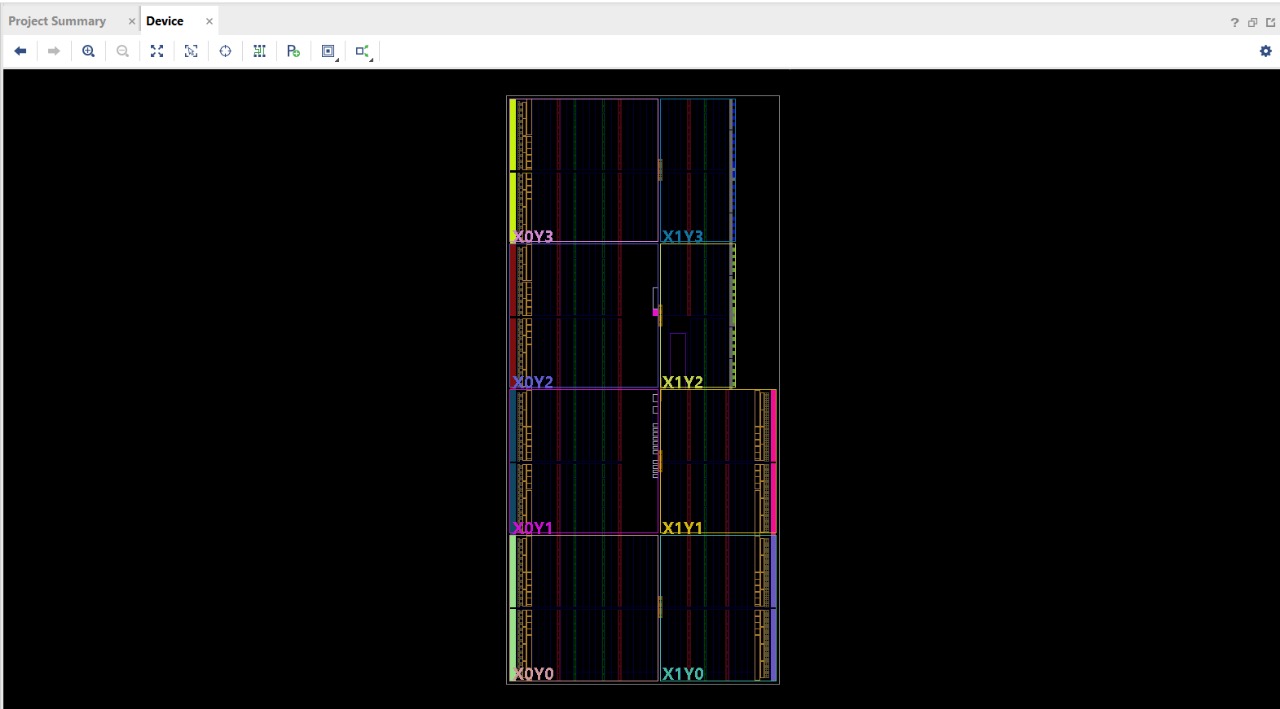

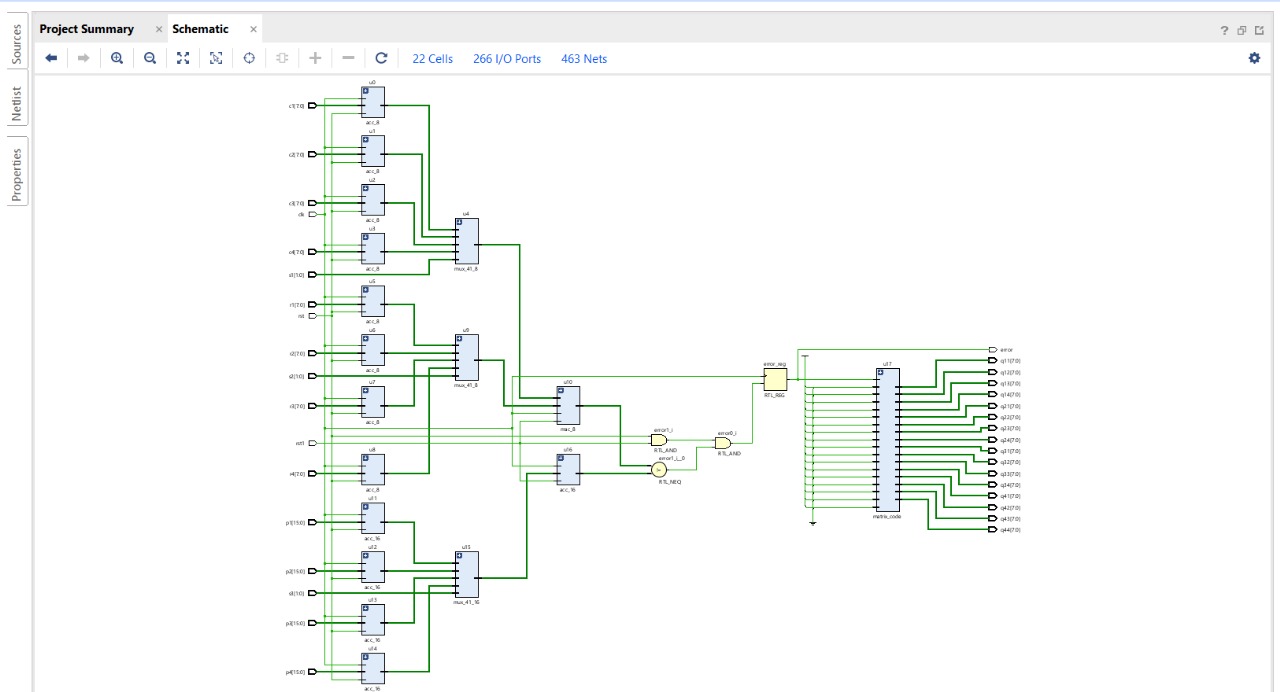

FPGA Simulation Results

Hardware synthesis and simulation results from Xilinx Vivado platform

Explore Project Structure

Verilog Code

21 HDL files across 4 modules (ABFT, Combined, Light ABFT, MC)

Simulation Outputs

4 high-resolution images showing simulation results and schematics

System Diagrams

Block diagrams and architectural schematics of the fault-tolerant system

IEEE Publication

Research paper published at IEEE ICCCNT 2025, IIT Indore